深圳市大源实业科技有限公司

经营,集成电路。为航空航天,雷达船舶,工业控制,石油测井,铁路电力,实验,

医疗器械,通信工程,仪器仪表,科研,等高科技行业提供配套服务。

主营品牌:MICROCHIP, TI, XILINX, LINEAR , HITTITE, MINI, MAXIM, TST, IDT, MACOM , NXP, ON, INTERSIL,等。

我们有代理渠道价格, 常年备有大量现货库存, 并接受订货服务!

多年来我们一直本着务实的态度,以只做原装现货质量,而赢得市场同行的好评,

并为国内多家厂商提供各种元器件配套服务,与之建立了长期的合作关系,

良好的信誉稳定的供货渠道,赢得了众多客户的信赖与支持,我们用诚信和人性化的服务与客户一起发自壮大。

公司宗旨:只做原装 诚实守信 长期合作!!!

联系人: 龙小姐

联系电话 :0755-84507670 13392442132(微信同步)

QQ号:1714298183

产品概述

|

产品型号

|

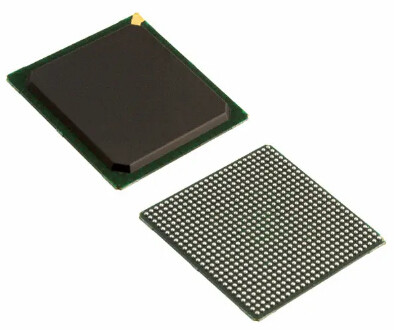

XC6SLX100-3FGG676C

|

|

描述

|

IC FPGA 480 I / O 676FBGA

|

|

分类

|

集成电路(IC),嵌入式FPGA(现场可编程门阵列)

|

|

生产厂家

|

Xilinx公司

|

|

系列

|

Spartan®-6 LX

|

|

部分状态

|

活性

|

|

电压-电源

|

1.14V~1.26V

|

|

工作温度

|

0°C~85°C(TJ)

|

|

包/箱

|

676-BGA

|

|

供应商设备包

|

676-FBGA(27x27)

|

|

基础部件号

|

XC6SLX100

|

产品图片

XC6SLX100-3FGG676C

规格参数

|

可编程逻辑类型

|

现场可编程门阵列

|

|

符合REACH标准

|

是

|

|

符合欧盟RoHS标准

|

是

|

|

状态

|

活性

|

|

时钟频率-最大值

|

862.0 MHz

|

|

CLB-Max的组合延迟

|

0.21 ns

|

|

JESD-30代码

|

S-PBGA-B676

|

|

JESD-609代码

|

E1

|

|

总RAM位数

|

4939776

|

|

CLB数量

|

7911.0

|

|

输入数量

|

480.0

|

|

逻辑单元的数量

|

101261.0

|

|

输出数量

|

480.0

|

|

终端数量

|

676

|

|

工作温度-最小值

|

0℃

|

|

工作温度-最高

|

85℃

|

|

组织

|

7911 CLBS

|

|

峰值回流温度(℃)

|

250

|

|

电源

|

1.2,2.5 / 3.3

|

|

资格状态

|

不合格

|

|

坐姿高度-最大

|

2.44毫米

|

|

子类别

|

现场可编程门阵列

|

|

电源电压

|

1.2 V

|

|

电源电压-最小值

|

1.14 V

|

|

电源电压-最大值

|

1.26 V

|

|

安装类型

|

表面贴装

|

|

技术

|

CMOS

|

|

温度等级

|

其他

|

|

终端完成

|

锡/银/铜(Sn96.5Ag3.0Cu0.5)

|

|

终端表格

|

球

|

|

终端间距

|

1.0毫米

|

|

终端位置

|

底部

|

|

时间@峰值回流温度-最大值(s)

|

三十

|

|

长度

|

27.0毫米

|

|

宽度

|

27.0毫米

|

|

包装体材料

|

塑料/环氧树脂

|

|

包裹代码

|

BGA

|

|

包等价代码

|

BGA676,26X26,40

|

|

包装形状

|

广场

|

|

包装风格

|

网格阵列

|

|

制造商包装说明

|

27 X 27 MM,1 MM PITCH,LEAD FREE,FBGA-676

|

环境与出口分类

|

无铅状态/ RoHS状态

|

无铅/符合RoHS标准

|

|

湿度敏感度等级(MSL)

|

3(168小时)

|

特点

-

交错的垫

-

高达3.2 Gb /s

-

热插拔合规性

-

专为低成本而设计

-

多个高效的集成块

-

优化的I / O标准选择

-

大批量塑料线焊包装

-

静态和动态功率低

-

Spartan-6 LX FPGA:逻辑优化

-

45纳米工艺针对成本和低功耗进行了优化

-

休眠掉电模式,实现零功耗

-

多电压,多标准SelectIO™接口组

-

每个差分I / O的数据传输速率高达1,080 Mb / s

-

可选输出驱动,每个引脚最高24 mA

-

3.3V至1.2VI / O标准和协议

-

低成本HSTL和SSTL存储器接口

-

可调节的I / O转换速率可提高信号完整性

-

LXT FPGA中的高速GTP串行收发器

-

用于PCI Express设计的集成端点模块(LXT)

-

低成本PCI®技术支持兼容33 MHz,32位和64位规范。

-

高效的DSP48A1切片

-

高性能算术和信号处理

-

快速18 x 18乘法器和48位累加器

-

流水线和级联功能

-

预加法器以协助过滤器应用程序

-

集成内存控制器块

-

DDR,DDR2,DDR3和LPDDR支持

-

数据速率高达800 Mb / s(峰值带宽为12.8 Gb / s)

-

具有独立FIFO的多端口总线结构可减少设计时序问题

-

丰富的逻辑资源和更高的逻辑容量

-

可选的移位寄存器或分布式RAM支持

-

高效的6输入LUT可提高性能并最大限度地降低功耗

-

具有双触发器的LUT用于管道中心应用

-

Block RAM具有广泛的粒度

-

具有字节写使能的快速Block RAM

-

18 Kb块,可选择编程为两个独立的9 Kb Block RAM

-

时钟管理平铺(CMT)以提高性能

-

低噪音,灵活的时钟

-

数字时钟管理器(DCM)消除了时钟偏差和占空比失真

-

用于低抖动时钟的锁相环(PLL)

-

具有同时乘法,除法和相移的频率合成

-

十六个低偏移全局时钟网络

-

简化配置,支持低成本标准

-

2针自动检测配置

-

业界领先的IP和参考设计

-

广泛的第三方SPI(最高x4)和NOR闪存支持

-

功能丰富的Xilinx Platform Flash和JTAG

-

MultiBoot支持使用看门狗保护进行多比特流的远程升级

-

增强了设计保护的安全性

-

用于设计验证的唯一设备DNA标识符

-

大型设备中的AES比特流加密

-

挂起模式通过多引脚唤醒,控制增强来维持状态和配置

-

通过增强的低成本MicroBlaze™软处理器实现更快的嵌入式处理

-

高速接口包括:串行ATA,Aurora,1G以太网,PCI Express,OBSAI,CPRI,EPON,GPON,DisplayPort和XAUI